Project profile

Spain, France, Germany, Italy, Greece, Sweden

01/04/2022 - 31/03/2024

Goals

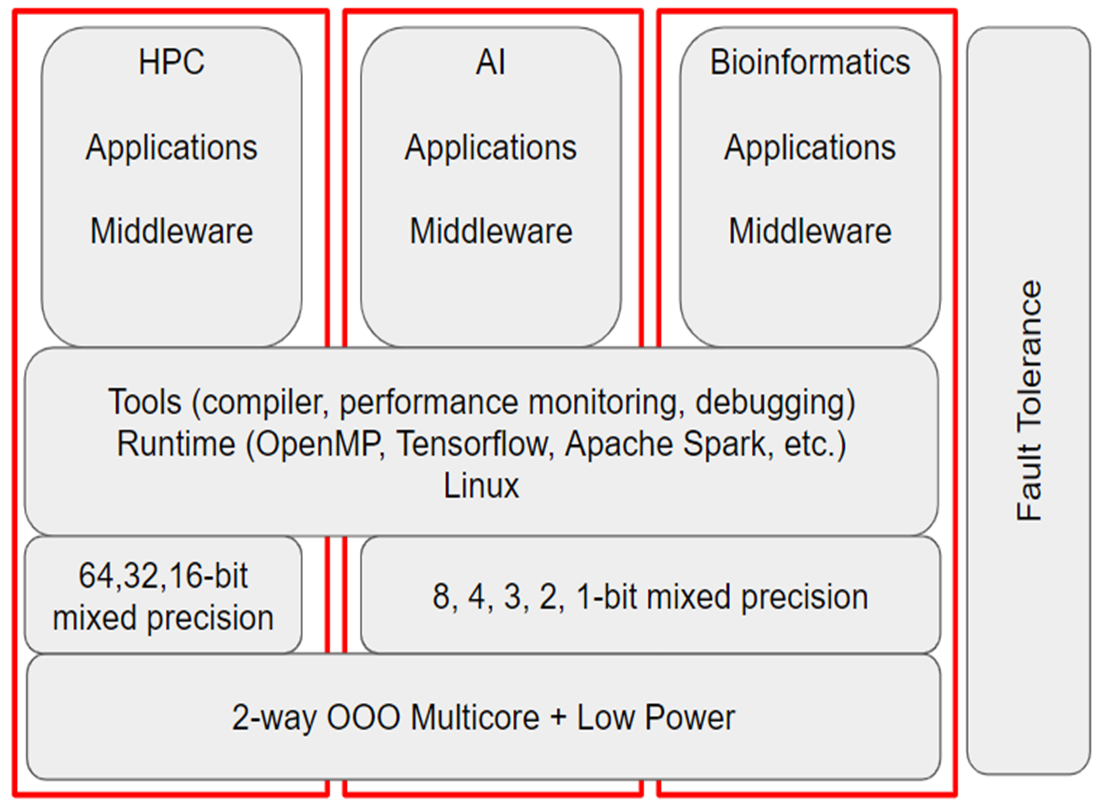

- Build a novel open source out-of-order execution processor based on RISC-V and matching accelerators

- Deliver the first completely open source European HW and system SW stack

- Combine pre-existing IP with project-developed, innovative IP building blocks

- Achieve highest energy efficiency, extreme scalability and straightforward extensibility for uses in HPC, AI/ML and embedded computing

- Employ HW/SW co-design to achieve high end-to-end application performance and system energy efficiency

- Produce architectural & FPGA-based simulations plus two ASIC tape-outs

Status and Results

- Fully functional IP blocks designed for or all architecture components (CPU cores, accelerators, reduced-precision units, caches, network-on-a-chip, peripherals)

- Integration and verification of IP blocks towards the first tape-out

- FPGA-based simulation successfully running bare-metal applications

- Complete specification of a node PCB and package for the first tape-out

- Operating system ready to be ported to the eProcessor system

- Significant advances in porting and optimising libraries and programming models

- Application use cases ported to RISC-V with clearly defined optimisation plans

- Development of a complete suite of microbenchmarks to evaluate eProcessor architecture components

Copyright @ eProcessor