Project profile

Germany, Greece, France, Spain, Sweden, Belgium, Switzerland, UK

01/04/2021 - 31/03/2024

Goals

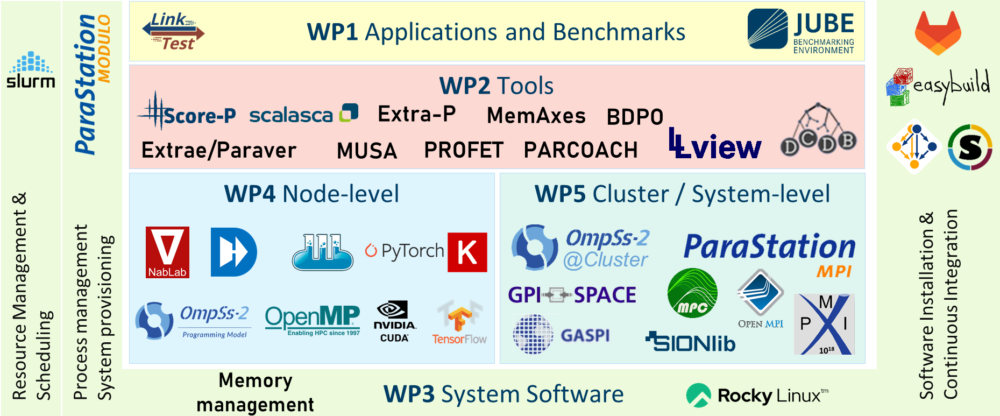

- Co-Design a SW stack for future European Exascale Systems and release it in production-ready quality

- Provide tools for mapping complex applications on heterogeneous & modular supercomputer architectures

- Support emerging memory technologies and enable efficient data placement on memory hierarchies

- Extract maximum performance from systems and improve performance portability

Motivation

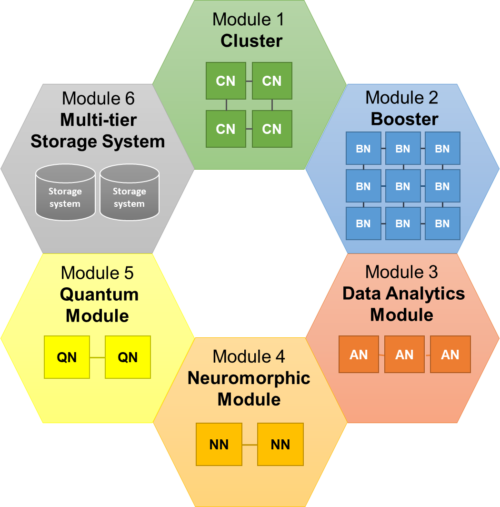

- HPC systems are highly heterogeneous

- Heterogeneity in processor, memory and network

- Different codes run better on different components

- Programming models might be vendor-specific

- This puts a burden on application developers, who must:

- Understand very well their codes and the HW

- Decide where to run each part of their codes

- Port codes to different technologies

- Optimise codes for different platforms

- DEEP-SEA simplifies and automates these tasks and provides near-production quality solutions

Copyright © Forschungszentrum Jülich

Status / Highlights

- Co-design process resulted in definition of SW stack

- Optimisation Cycles capture and streamline mapping, performance analysis and optimization tasks

- Continuous Integration (CI) ensures SW stack consistency

- 2nd SW stack version rolled out end of 2022

- Seven co-design applications test & validate SW stack components, and guide further development

Copyright © Forschungszentrum Jülich